Jedec은 주요 대역폭 및 효율 업그레이드로 HBM4 메모리 표준을 완료합니다.

Jadec 게시 AI 워크로드, 고성능 컴퓨팅 및 고급 데이터 센터 환경의 빠르게 성장하는 요구 사항을 유지하기위한 새로운 메모리 표준 인 Jesd238에 따른 공식 HBM4 (높은 대역폭 메모리 4) 사양. 새로운 표준은 데이터 집약적 응용 프로그램이 계속 발전함에 따라 메모리 대역폭, 용량 및 효율성을 향상시키려는 아키텍처 변경 및 인터페이스 업그레이드를 소개합니다.

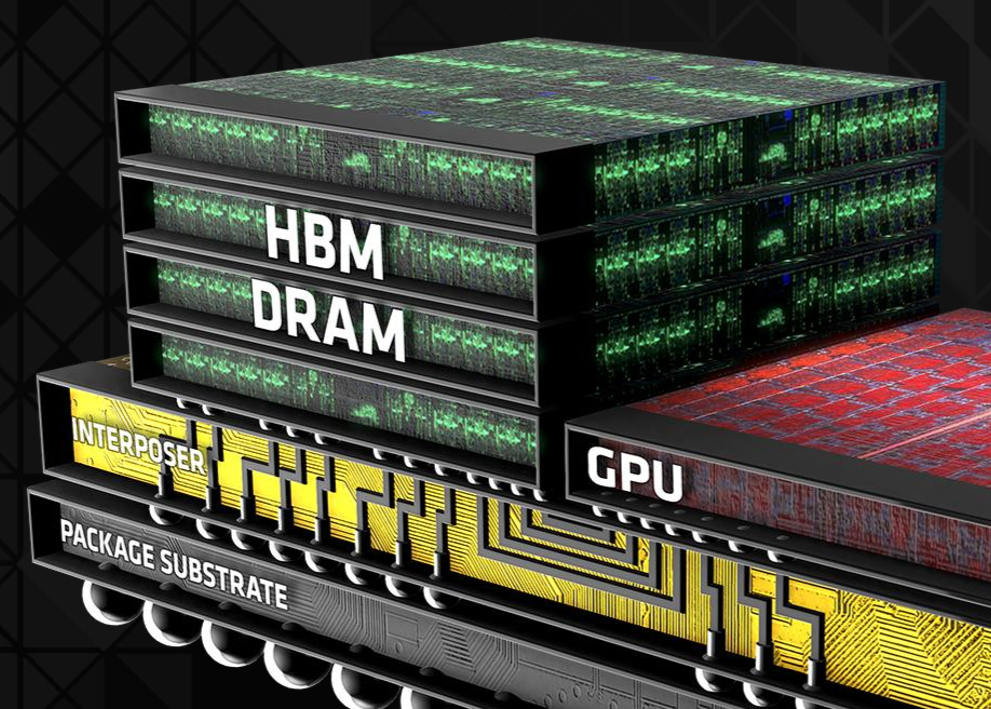

HBM4는 HBM 제품군의 특징 인 수직 적용 DRAM Dies의 사용을 계속하지만 대역폭, 효율성 및 설계 유연성의 상당한 발전으로 전임자 HBM3보다 많은 개선 사항을 제공합니다. 2048 비트 인터페이스에서 최대 8GB/s의 전송 속도를 지원하여 최대 2TB/s의 총 대역폭을 제공합니다. 주요 업그레이드 중 하나는 HBM3에서 16 개에서 HBM4의 16 개에서 32 개까지 스택 당 독립 채널의 두 배가된다는 것입니다. 이 확장은 메모리 작업에서 유연성과 병렬 처리를 향상시킬 수 있습니다.

전력 효율 측면에서 JESD270-4 사양은 VDDQ 옵션 0.7V, 0.75V, 0.8V 또는 0.9V 및 VDDC 옵션 1.0V 또는 1.05V를 포함한 다양한 공급 업체 별 전압 레벨에 대한 지원을 도입합니다. 이러한 조정은 다양한 시스템 요구 사항에 따라 전력 소비량을 낮추고 에너지 효율을 향상시키는 데 기여한다고합니다. HBM4는 또한 기존 HBM3 컨트롤러와의 호환성을 유지하므로 단일 컨트롤러가 메모리 표준으로 작동 할 수 있습니다. 이 거꾸로 호환성은 채택을 완화시키고보다 유연한 시스템 설계를 가능하게합니다.

또한 HBM4는 Row-Hammer 완화를 향상시키고 더 강력한 신뢰성, 가용성 및 서비스 가능성 (RAS) 기능을 지원하는 DRFM (Directed Reshend Management)을 통합합니다. 용량 전면에서 HBM4는 4 높이에서 16 높이 범위의 스택 구성을 지원하며 DRAM 다이 밀도는 24GB 또는 32GB입니다. 이를 통해 32GB 16 높이의 스택을 사용하여 64GB의 큐브 용량이 높아져 워크로드를 요구하는 메모리 밀도가 높아질 수 있습니다.

HBM4의 주목할만한 아키텍처 변화는 동시성을 향상시키고 대기 시간을 줄이기 위해 설계된 명령 및 데이터 버스의 분리입니다. 이 수정은 AI 및 HPC 워크로드에서 널리 퍼져있는 다 채널 작업의 성능을 향상시키는 것을 목표로합니다. 또한 HBM4는 새로운 물리적 인터페이스 및 신호 무결성 개선을 통합하여 더 빠른 데이터 속도와 더 큰 채널 효율을 지원합니다.

HBM4의 개발에는 표준의 공식에 기여한 삼성, 미크론, SK Hynix를 포함한 주요 업계 선수들 사이의 협력이 포함되었습니다. 이 회사들은 가까운 시일 내에 HBM4 호환 제품을 선보일 것으로 예상되며, 삼성은 2025 년까지 AI Chipmakers 및 Hyperscalers의 증가하는 수요를 충족시키기 위해 생산을 시작할 계획을 나타냅니다.

AI 모델과 HPC 애플리케이션이 더 큰 계산 리소스를 요구함에 따라 대역폭이 높고 용량이 더 높아지는 메모리에 대한 기술적 필요가 증가하고 있습니다. HBM4 표준의 도입은 데이터 처리량을 처리하고 이러한 워크로드와 관련된 처리 문제를 처리하도록 설계된 차세대 메모리 기술에 대한 사양을 간략히 설명하여 이러한 요구 사항을 해결해야합니다.

Post Comment